# 16-Segment LED Nixie tube Driver and Keyboard Controller

# **CH454**

Datasheet Version: 1E http://wch.cn

## 1. Overview

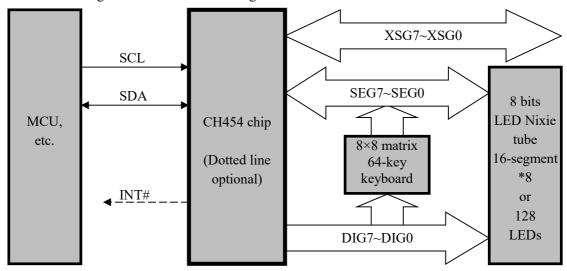

CH454 is a LED Nixie tube display driver and keyboard scan control chip. CH454 has a built-in clock oscillation circuit, which can dynamically drive 8 16-segment LED Nixie tubes or 128 LEDs, support 11-segment, 14-segment, 16-segment × 8 and 17-segment × 7, etc. and can also scan the keyboard with 64 keys. CH454 exchanges data with a MCU through a 2-wire serial interface.

#### 2. Features

### 2.1. Display Driver

- Built-in current driving stage, segment current not less than 20mA, word current not less than 150mA.

- Dynamic display scanning control, direct drive of 8-bit 16-segment LED Nixie tubes or 128 LEDs.

- Digital independent flash control of each LED Nixie tube, and the slow and fast scintillation speed can be selected.

- Provide 16-level brightness control through duty ratio setting.

- Partial segment addressing, independently control the first 64 LEDs or ON and OFF of the first 8 segments of each LED Nixie tube.

- Scan limit control, support 1 ~ 8 LED Nixie tubes, and allocate scan time only to the valid LED Nixie tubes.

- The word drive output polarity can be selected to facilitate external expansion of drive voltage and current.

#### 2.2. Keyboard Control

- Built-in 64-key keyboard controller, based on 8×8 matrix keyboard scan.

- Built-in pull-down resistor of key status input, built-in jitter suppression circuit.

- Keyboard interrupt output, active at low level.

- Provide key release flag bit for query key to be pressed down and released.

- Support key wake-up, CH454 in low-power and power saving state can be awakened by some keys.

#### 2.3. Miscellaneous

- Two-wire serial interface, compatible with I<sup>2</sup>C bus, saving pins.

- Built-in clock oscillator circuit, no need to provide external clock or external oscillator components, more anti-interference.

- Support low-power sleep, save power, can be waked up by key or command operation.

- Provide SOP28 and SDIP32 lead-free package, and be compatible with RoHS.

# 3. Package

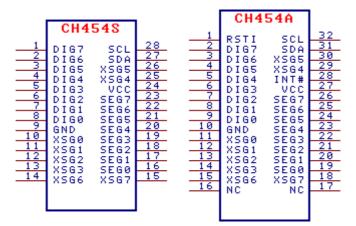

| Package | Width   |        | Pitch        | of Pin | Instruction of Package                     | Ordering information |

|---------|---------|--------|--------------|--------|--------------------------------------------|----------------------|

| SOP28   | 7.62mm  | 300mil | 1.27mm 50mil |        | Standard 28-pin patch                      | CH454S               |

| SDIP32  | 10.16mm | 400mil | 1.78mm       | 70mil  | Narrow spacing 32-pin dual in-line package | CH454A               |

Notes: Based on the considerations of the cost and supply cycle, chip with patch package is recommended.

# 4. Pins

| SOP28<br>Pin No.            | SDIP32<br>Pin No.           | Pin<br>Name   | Pin Type                      | Pin description                                                                                                                                  |

|-----------------------------|-----------------------------|---------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 24                          | 27                          | VCC           | Power                         | Positive power supply, continuous current not less than 150mA                                                                                    |

| 9                           | 10                          | GND           | Power                         | Common ground, continuous current not less than 150mA                                                                                            |

| 16~23                       | 19~26                       | SEG0<br>~SEG7 | Three-status output and input | Segment drive of LED Nixie tube, active at high level  Keyboard scan input, active at high level, built-in pull-down resistor                    |

| 10~13,<br>25, 26,<br>14, 15 | 11~14,<br>29, 30,<br>15, 18 | XSG0<br>~XSG7 | Three-status output and input | Extension segment drive of LED Nixie tube, active at high level, Universal I/O input and output, built-in weak pull-up resistor                  |

| 8~1                         | 9~2                         | DIG0<br>~DIG7 | Output                        | Word drive of LED Nixie tube, active at low level<br>Keyboard scan output, active at high level,<br>DIG7 doubles as the segment 17 driver of the |

|      |        |      |                             | LED Nixie tube                                                                    |

|------|--------|------|-----------------------------|-----------------------------------------------------------------------------------|

| 27   | 31     | SDA  | Open-drain output and input | Data input and output of 2-wire serial interface, Built-in pull-up resistor       |

| 28   | 32     | SCL  | Input                       | Data clock of two-wire serial interface, built-in pull-up resistor                |

| None | 28     | INT# | Open-drain output           | Keyboard interrupt output, built-in pull-up resistor, active at low level         |

| None | 1      | RSTI | Input                       | External manual reset input, active at high level,<br>built-in pull-down resistor |

| None | 16, 17 | NC   | Idle pin                    | Reserved pins. Do not connect them                                                |

# 5. Function Specification

#### 5.1. General Specification

For data in this manual, those ending with B are binary numbers and those ending with H are hexadecimal numbers. Otherwise, they are decimal numbers. The bit marked as x indicates that the bit can be any value.

### 5.2. Display Driver

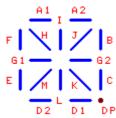

CH454 uses dynamic scanning driver for the LED Nixie tube and LED. The order is from DIG0 to DIG7. When one pin sinks the current, the other pins do not sink the current. The CH454 has an internal current drive stage, which can directly drive 0.5 to 1 inch common cathode LED Nixie tube. For the 7-segment or 8-segment LED Nixie tube, the segment drive pins SEG6~SEG0 correspond to the segment G ~ segment A of the LED Nixie tube, and the segment drive pin SEG7 corresponds to the segment 8 decimal point of the LED Nixie tube. For the 16-segment LED Nixie tube, SEG7~SEG0 and XSG7~XSG0 should be used to drive each segment. For 17-segment LED Nixie tube, DIG7 also needs to be used to drive the segment 17 decimal point and the scanning limit must be less than 8. For 11-segment or 14-segment LED Nixie tubes, undesired pins can be suspended arbitrarily in SEG7 ~ SEG0 and XSG7 ~ XSG0. For the 17-segment LED Nixie tubes, the word drive pins DIG6 ~ DIG0 are connected to the cathodes of 7 LED Nixie tubes respectively. For LED Nixie tubes with less than 17 segments, the word-driven pins DIG7 ~ DIG0 are connected to the cathodes of 8 LED Nixie tubes respectively. The CH454 can also be connected to a 16×8 matrix LED array or 128 independent LEDs. CH454 can change the word drive output polarity so as to directly drive the common anode LED Nixie tube, or support the common anode LED Nixie tube through the external inverting driver, or support the large size LED Nixie tube with the external high power valve.

The CH454 supports scan limit control and allocates scan time only to the valid LED Nixie tubes. When the scan limit is set to 1, the unique LED Nixie tube DIG0 will get all the dynamic drive time, thus equating to the static drive. When the scan limit is set to 8, the 8 LED Nixie tubes DIG7~DIG0 will each get 1/8 of the dynamic drive time. When the scan limit is set to 4, the 4 LED Nixie tubes DIG3~DIG0 will each get 1/4 of the dynamic drive time. At this time, the average drive current of each LED Nixie tube will be doubled compared with the scan limit of 8, so reducing the scan limit can improve the display brightness of the LED Nixie tube. When driving a 17-segment LED Nixie tube, the scanning limit must be less than or equal to 7.

CH454 has 8 16-bit data registers, which are used to store 8 word data, corresponding to 8 LED Nixie tubes or 8 groups of LEDs driven by CH454, 16 LEDs in each group. When the data bit is 1, the segment of the corresponding LED Nixie tube or LED will be on. When the data bit is 0, the segment of the corresponding LED Nixie tube or LED will be off.

CH454 supports partial segment addressing and can be used to independently control any one of 64 LEDs or a specific segment in a LED Nixie tube (for example, a decimal point). The segment addressing

sequence is the same as the keyboard addressing, from 00H to 3FH. When the segment position of an address is set to 1 with the command of "Segment Addressing Set to 1", the segment of the LED or LED Nixie tube corresponding to that address will be ON. This operation does not affect the status of any other LED or other segments of the LED Nixie tube. CH454 segment addressing only supports 8×8 matrix driven by SEG7 ~ SEG0 pins, while segment addressing is not supported for the LED or LED Nixie tube segments driven by XSG7 ~ XSG0 pins.

The following diagram shows the segment name of the 7-segment and 8-segment LED Nixie tubes

The following diagram shows the segment name of the 16-segment and 17-segment LED Nixie tubes

# 5.3. Keyboard Scan

CH454 keyboard scan feature supports an 8×8 matrix 64-key keyboard. During keyboard scan, pins DIG7~DIG0 are used for the column scan output, and SEG7~SEG0 pins have internal pull-down resistors for the line scan input.

CH454 periodically inserts keyboard scan during the display driver scan. During keyboard scan, the pins DIG7~DIG0 output high level in sequence from DIG0 to DIG7, and the remaining 7 pins output low level. The outputs of the pins SEG7-SEG0 are disabled. When no key is pressed, SEG7-SEG0 are pulled down to low level. When a key is pressed, for example, the key connecting DIG3 and SEG4 is pressed, SEG4 detects high level when DIG3 outputs high level. In order to avoid error code caused by key jitter or external interference, CH454 performs two scans. Only when the results of two keyboard scans are the same, the key will be confirmed to be valid. If CH454 detects a valid key, the key code will be recorded, and active low keyboard interrupt will be generated through INT# pin. At this time, the MCU can read the key code through the serial interface. CH454 does not generate any keyboard interrupt until a new valid key is detected. CH454 does not support combination key, that is, two or more keys cannot be pressed at the same time. If multiple keys are pressed at the same time, the key with the smaller key code will take precedence. In the case of time priorities, the one firstly pressed is valid.

The key code provided by CH454 is 8 bits. Bit2 ~ bit0 are column scanning codes. Bit5 ~ bit3 are line scanning codes. Bit6 is status code (key pressed is 1, and key released is 0). Bit7 is 0. For example, when the key connecting DIG3 and SEG4 is pressed, the key code is 01100011B or 63H. After the key is released, the key code is usually 00100011B or 23H (or other values, but certainly less than 40H), where the column scan code corresponding to DIG3 is 011B, and the line scan code corresponding to SEG4 is 100B. The MCU can read the key code at any time, but it generally read the key code when CH454 detects a valid key and produces keyboard interrupt. At this time, the bit6 of the key code is always 1. In addition, if you need to know when the key is released, the MCU can read the key code regularly by inquiry until the bit 6 of the key code is 0.

The following table shows 8×8 matrix sequential addressing between DIG7~DIG0 and SEG7-SEG0, which are not only the sequence addressing, but also the array addressing of the LED Nixie tube segments and LEDs. As the key code is 8-bit, the bit 6 is always 1 when the key is pressed. When the key is pressed, the actual key code provided by CH454 is the key address in the table plus 40H, that is, the key code should be 40H-7FH.

| Addressing | DIG7 | DIG6 | DIG5 | DIG4 | DIG3 | DIG2 | DIG1 | DIG0 |

|------------|------|------|------|------|------|------|------|------|

| SEG0       | 07H  | 06H  | 05H  | 04H  | 03H  | 02H  | 01H  | 00H  |

| SEG1       | 0FH  | 0EH  | 0DH  | 0CH  | 0BH  | 0AH  | 09H  | 08H  |

| SEG2       | 17H  | 16H  | 15H  | 14H  | 13H  | 12H  | 11H  | 10H  |

| SEG3       | 1FH  | 1EH  | 1DH  | 1CH  | 1BH  | 1AH  | 19H  | 18H  |

| SEG4       | 27H  | 26H  | 25H  | 24H  | 23H  | 22H  | 21H  | 20H  |

| SEG5       | 2FH  | 2EH  | 2DH  | 2CH  | 2BH  | 2AH  | 29H  | 28H  |

| SEG6       | 37H  | 36H  | 35H  | 34H  | 33H  | 32H  | 31H  | 30H  |

| SEG7       | 3FH  | 3EH  | 3DH  | 3CH  | 3BH  | 3AH  | 39H  | 38H  |

#### 5.4. Serial Interface

CH454 2-wire serial interface includes 3 signal lines: serial data clock input line SCL, serial data input and output line SDA, and the optional interrupt output line INT#. Wherein, SCL is the input signal line with a pull-up resistor and at high level by default. SDA is a semi-bidirectional signal line with a pull-up resistor and at high level by default. INT# is an open-drain output signal line with a pull-up resistor, it is at high level by default.

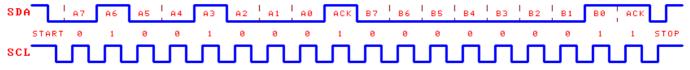

SDA is used for serial data input and output. The high level represents bit data 1, and the low level represents bit data 0. The sequence of serial data input is that the high bit is at the front and the low bit is at the back.

SCL is used to provide a serial clock, CH454 inputs data from SDA during high level after its rising edge and outputs data from SDA during low level after its falling edge.

INT# is used for keyboard interrupt output. INT# outputs keyboard interrupt active at low level when CH454 detects a valid key. After the MCU is interrupted, it sends out the read key code command, and CH454 recovers the INT# to high level and outputs the key code from SDA. The MCU gets a byte of data from SDA, i.e. the key code.

SDA falling edge occurring during the SCL high level period is defined as the start signal of the serial interface, and SDA rising edge occurring during the SCL high level period is defined as the stop signal of the serial interface. CH454 receives and analyzes the command only after detecting the start signal. Therefore, when the MCU I/O pin resources are limited, SCL pins can be shared with other interface circuits as long as the SDA pin state remains unchanged.

The communication process between the MCU and CH454 is always divided into six steps. According to the operation direction of MCU, it is divided into two types: write operation for output data and read operation for input data. For the specific process, please refer to Example Program.

Write operation consists of six steps: output start signal, output byte 1, response 1, output byte 2, response 2 and output stop signal. Among them, the start signal and the stop signal are as mentioned above, response 1 and response 2 are usually 0, output byte 1 and output byte 2 respectively contain 8 data bits, namely, one byte of data.

Read operation consists of six steps: output start signal, output byte 1, response 1, input byte 2, response 2 and output stop signal. Among them, the start signal and the stop signal are as mentioned above, response 1 and response 2 are usually 0, output byte 1 and input byte 2 respectively contain 8 data bits, namely, one byte of data.

The following figure shows an example of write operation. The byte 1 is 01001000B, namely, 48H. The byte 2 is 00000001B, namely, 01H.

# 6. Operation Commands

Start signal, stop signal and response are the same for each operation command of CH454, except that the data of output byte 1 and byte 2 are different and that byte 2 is transmitted in different direction. Bit 15 and bit 14 of byte 1 are fixed as 0 and 1, bit 8 is the read/write direction bit R/-W. If the bit is 0, perform the write operation and write the byte 2 into CH454. If the bit is 1, perform the read operation and read the byte 2 from CH454.

The serial data corresponding to each operation command of CH454 is listed in the table below. The bit marked with a name indicates that the bit has a corresponding register in the CH454 chip, and its data changes according to different operation commands. Data marked in gray is the return of a read operation.

| Byte 1, bit 15=0, bit 14=           |           |           |           |           | mands. Data marked in gray is the return of a read operation. |          |                                                                       |                                                                       |          |                   |                      |          |          |          |

|-------------------------------------|-----------|-----------|-----------|-----------|---------------------------------------------------------------|----------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|----------|-------------------|----------------------|----------|----------|----------|

| Operation                           |           |           |           |           |                                                               |          |                                                                       | , ,                                                                   |          | Byt               | e 2                  |          | ı        |          |

| command                             | Bit<br>13 | Bit<br>12 | Bit<br>11 | Bit<br>10 | Bit<br>9                                                      | Bit<br>8 | Bit 7                                                                 | Bit 6                                                                 | Bit 5    | Bit 4             | Bit 3                | Bit 2    | Bit 1    | Bit 0    |

| Segment<br>addressing<br>clear to 0 | 0         | 0         | 0         | 0         | 1                                                             | 0        | 1                                                                     | 0 BIT_ADDR                                                            |          |                   |                      |          |          |          |

| Segment addressing set to 1         | 0         | 0         | 0         | 0         | 1                                                             | 0        | 1                                                                     | 1 BIT_ADDR                                                            |          |                   |                      |          |          |          |

| Chip internal reset                 | 0         | 0         | 0         | 1         | 0                                                             | 0        | 0                                                                     | 0                                                                     | 0        | 0                 | 0                    | 0        | 0        | 1        |

| Enter sleep state                   | 0         | 0         | 0         | 1         | 0                                                             | 0        | 0                                                                     | 0                                                                     | 0        | 0                 | 0                    | 0        | 1        | 0        |

| Set auxiliary parameters            | 0         | 0         | 0         | 1         | 0                                                             | 0        | 1                                                                     | 0                                                                     | 1        | 0                 | 0                    | 0        | 0        | LMTC     |

| Customized<br>BCD code              | 0         | 0         | 0         | 1         | 1                                                             | 0        | 1                                                                     | SELF_BCD                                                              |          |                   |                      |          |          |          |

| Set system parameters               | 0         | 0         | 1         | 0         | 0                                                             | 0        | XGPO                                                                  | XSOE                                                                  | 0        | SSPD              | DPLR                 | 0        | KEYB     | DISP     |

| Set display parameters              | 0         | 0         | 1         | 0         | 1                                                             | 0        | MODE                                                                  | LIMIT INTENSITY                                                       |          |                   |                      |          |          |          |

| Set flash control                   | 0         | 0         | 1         | 1         | 0                                                             | 0        | D7S                                                                   | D6S                                                                   | D5S      | D4S               | D3S                  | D2S      | D1S      | D0S      |

| Load word data<br>0L                | 0         | 1         | 0         | 0         | 0                                                             | 0        | DIG DA                                                                | ATA0 L0                                                               | O, the c | orrespoi<br>lower | _                    | ord data | of DIG   | 0 is the |

| Load word data<br>1L                | 0         | 1         | 0         | 0         | 1                                                             | 0        | DIG_1                                                                 | DATA1_                                                                | _        | -                 | oonding<br>er 8 bits |          | ata of D | IG1 is   |

| Load word data<br>2L                | 0         | 1         | 0         | 1         | 0                                                             | 0        | DIG_                                                                  | DATA2_                                                                | _        | -                 | oonding<br>er 8 bits |          | ata of D | IG2 is   |

| Load word data 3L                   | 0         | 1         | 0         | 1         | 1                                                             | 0        | DIG_                                                                  | DATA3_                                                                |          |                   | oonding<br>er 8 bits |          | ata of D | IG3 is   |

| Load word data<br>4L                | 0         | 1         | 1         | 0         | 0                                                             | 0        | DIG_1                                                                 | DATA4_                                                                | _        | -                 | oonding<br>er 8 bits |          | ata of D | IG4 is   |

| Load word data<br>5L                | 0         | 1         | 1         | 0         | 1                                                             | 0        | DIG_DATA5_LO, the corresponding word data of DIG5 is the lower 8 bits |                                                                       |          |                   |                      | IG5 is   |          |          |

| Load word data<br>6L                | 0         | 1         | 1         | 1         | 0                                                             | 0        | DIG_1                                                                 | DIG_DATA6_LO, the corresponding word data of DIG6 is the lower 8 bits |          |                   |                      |          |          | IG6 is   |

| Load word data<br>7L                | 0         | 1         | 1         | 1         | 1                                                             | 0        | DIG_1                                                                 | DATA7_                                                                | _        | -                 | onding<br>er 8 bits  |          | ata of D | IG7 is   |

| Load word data    | 1 | 0 | 0 | 0 | 0 | 0 | DIG_D                                                                  | ATA0_F         | II, the c  | orrespo | nding w   | ord data | a of DIG | 0 is the  |

|-------------------|---|---|---|---|---|---|------------------------------------------------------------------------|----------------|------------|---------|-----------|----------|----------|-----------|

| 0H                | 1 | U | U | U | U | U |                                                                        |                |            | higher  | 8 bits    |          |          |           |

| Load word data    | 1 | 0 |   | 0 | 1 | _ | DIG D                                                                  | ATA1 F         | II, the c  | orrespo | nding w   | ord data | a of DIG | 1 is the  |

| 1H                | 1 | 0 | 0 | 0 | 1 | 0 | _                                                                      |                |            | higher  | 8 bits    |          |          |           |

| Load word data    |   |   |   | _ | _ |   | DIG D                                                                  | ATA2 F         | II, the c  | orrespo | nding w   | ord data | a of DIG | 2 is the  |

| 2Н                | 1 | 0 | 0 | 1 | 0 | 0 | _                                                                      | _              |            | higher  | _         |          |          |           |

| Load word data    |   |   |   |   |   |   | DIG D                                                                  | ATA3 F         | II. the c  |         |           | ord data | a of DIG | 3 is the  |

| 3H                | 1 | 0 | 0 | 1 | 1 | 0 | 210_2                                                                  |                | 11, 1110 0 | higher  | _         | 010 0000 | . 01 210 | 0 10 1110 |

| Load word data    |   |   |   |   |   |   | DIG D                                                                  | ΔΤΔ <b>4</b> Ι | II the c   |         |           | ord data | a of DIG | 4 is the  |

| 4H                | 1 | 0 | 1 | 0 | 0 | 0 | DIG_D                                                                  |                | 11, 1110 0 | higher  | _         | ora aaa  | . 01 D10 | i is the  |

| Load word data    |   |   |   |   |   |   | DIG D                                                                  | ΔΤΔ5 Ι         | II the c   |         |           | ord date | a of DIG | 5 is the  |

| 5H                | 1 | 0 | 1 | 0 | 1 | 0 | DIG_DATA5_HI, the corresponding word data of DIG5 is the higher 8 bits |                |            |         |           |          |          |           |

| Load word data    |   |   |   |   |   |   |                                                                        |                |            |         |           |          |          |           |

| 6H                | 1 | 0 | 1 | 1 | 0 | 0 | DIG_DATA6_HI, the corresponding word data of DIG6 is the higher 8 bits |                |            |         |           |          |          |           |

| Load word data    |   |   |   |   |   |   | DIG DATA7 HI, the corresponding word data of DIG7 is the               |                |            |         |           |          |          |           |

| Coad word data    | 1 | 0 | 1 | 1 | 1 | 0 | טוט_ט.                                                                 | AIA/_F         | 11, the C  | -       | _         | ora data | a of DIG | / is the  |

| Read SEG pin      | 0 | 0 | 0 | 0 | 1 | 1 | higher 8 bits SEG7 SEG6 SEG5 SEG4 SEG3 SEG2 SEG1 SEG0                  |                |            |         | SECO      |          |          |           |

|                   | 0 | 0 | 0 | 1 | 0 | 1 | XSG7                                                                   |                | XSG5       |         | XSG3      |          | XSG1     | XSG0      |

| Read XSG pin Read | U | U | U | 1 | U | 1 | ASG/                                                                   | ASGO           | ASGS       | A3U4    | ASGS      | ASGZ     | ASGI     | ASGU      |

| customized        | 0 | 0 | 0 | 1 | 1 | 1 | 0 SELF BCD                                                             |                |            |         |           |          |          |           |

| BCD code          | U | U | U | 1 | 1 | 1 | 0 SELI_BCD                                                             |                |            |         |           |          |          |           |

|                   |   |   |   |   |   |   |                                                                        |                |            |         |           |          |          |           |

| Read back         | 0 | 0 | 1 | 0 | 0 | 1 | VCDO                                                                   | VCOE           | 0          | CCDD    | DDID      | 0        | KEND     | DICD      |

| system            | 0 | 0 | 1 | 0 | 0 | 1 | XGPO                                                                   | XSOE           | 0          | SSPD    | DPLR      | 0        | KEYB     | DISP      |

| parameters        |   |   |   |   |   |   |                                                                        |                |            |         |           |          |          |           |

| Read back         | 0 | 0 | , |   |   | 1 | MODE                                                                   |                |            |         |           | D.M.     | NICITY   |           |

| displayed         | 0 | 0 | 1 | 0 | 1 | 1 | MODE                                                                   |                | LIMIT      |         |           | INTE     | NSITY    |           |

| parameters        |   |   |   |   |   |   |                                                                        |                |            |         |           |          |          |           |

| Read back         | 0 | 0 | 1 | 1 | 0 | 1 | D7S                                                                    | D6S            | D5S        | D4S     | D3S       | D2S      | D1S      | D0S       |

| flash control     | 0 | 0 | 1 | 1 | 1 | 1 | IZEX Z                                                                 | IZENI.         | 175375     | 175374  | 17.53.70  | 17.57.70 | 17.57.1  | IZENZO    |

| Read key code     | 0 | 0 | 1 | 1 | 1 | 1 | KEY7                                                                   |                | KEY5       |         | l         | KEY2     | KEY1     | KEY0      |

| Read back         | 0 | 1 | 0 | 0 | 0 | 1 | DIG DA                                                                 | ATA0 LO        | S, the c   | •       |           | ord data | of DIG   | 0 is the  |

| word data 0L      |   |   |   |   |   |   | 5.0                                                                    |                |            | lower   |           |          |          |           |

| Read back         | 0 | 1 | 0 | 0 | 1 | 1 | DIG_I                                                                  | DATA1_         |            |         |           |          | ata of D | lG1 is    |

| word data 1L      |   |   |   |   |   |   |                                                                        |                |            |         | er 8 bits |          |          |           |

| Read back         | 0 | 1 | 0 | 1 | 0 | 1 | DIG_I                                                                  | DATA2_         | ="         | _       | _         | word d   | ata of D | IG2 is    |

| word data 2L      |   |   |   |   |   |   |                                                                        |                |            |         | er 8 bits |          |          |           |

| Read back         | 0 | 1 | 0 | 1 | 1 | 1 | DIG_I                                                                  | DATA3_         | _          | •       |           |          | ata of D | IG3 is    |

| word data 3L      | Ů |   | Ť |   |   |   |                                                                        |                |            |         | er 8 bits |          |          |           |

| Read back         | 0 | 1 | 1 | 0 | 0 | 1 | DIG_DATA4_LO, the corresponding word data of DIG4 is                   |                |            |         |           |          |          |           |

| word data 4L      | Ů |   |   |   |   |   | the lower 8 bits                                                       |                |            |         |           |          |          |           |

| Read back         | 0 | 1 | 1 | 0 | 1 | 1 | DIG_DATA5_LO, the corresponding word data of DIG5 is                   |                |            |         |           |          |          |           |

| word data 5L      |   |   |   |   | - |   |                                                                        |                |            |         | er 8 bits |          |          |           |

| Read back         | 0 | 1 | 1 | 1 | 0 | 1 | DIG_I                                                                  | DATA6_         | ="         | _       | _         | word d   | ata of D | IG6 is    |

| word data 6L      |   |   |   | _ | Ľ | - |                                                                        |                |            |         | er 8 bits |          |          |           |

| Read back         | 0 | 1 | 1 | 1 | 1 | 1 | DIG_I                                                                  | DATA7_         | _          | •       |           |          | ata of D | IG7 is    |

| word data 7L      | Ŭ |   |   |   |   |   |                                                                        |                |            | the low | er 8 bits |          |          |           |

# **6.1. Chip internal reset**: 000100-00000001B

The internal reset command restores the registers and parameters of CH454 to the default state. When

the chip is powered on, CH454 is always reset. At this time, all registers are reset to 0 and all parameters are restored to the default values.

## **6.2. Enter Sleep State**: 000100-00000010B

The command to enter sleep state causes the CH454 to pause display driver and keyboard scan, and enter the low-power sleep state, thus saving electricity. CH454 in low-power sleep state can be waked up by any of the following two events. The first event is the detection of keys on SEG3-SEG0, and the valid key code is from 40H to 5FH. The second event is the detection of a state change in the SCL pin. Sleep and wake up operations themselves do not affect the working state of CH454.

# 6.3. Set System Parameters: 001000-[XGPO][XSOE]0[SSPD][DPLR]0[KEYB][DISP]B

"Set System Parameter Command" is used to set system-level parameters of CH454: display driver enable DISP, keyboard scanning enable KEYB, word drive output polarity DPLR, scintillation speed SSPD, XSG pin output enable XSOE, XSG pin working mode XGPO. Each parameter is controlled by 1-bit data. Please refer to the following table for details. For example: Command data 001000-01000001B represents that turn off keyboard scan function, enable display scan driver, and allow extended segment XSG output to support 16 segments. If XGPO is 1, then XSG pin is used for general-purpose input/output GPIO, and the I/O direction is set by XSOE. When it is 1, output the higher 8 bits DIG\_DATA0\_HI to XSG pins of DIG0 word data. If XGPO is 0 and XSOE is 1, then XSG pins used to extend the segment scan output, and support the 16-segment LED Nixie tube. If the scan LIMIT is less than or equal to 7 at this time, then DIG7 pins are used to drive the segment 17, which support 17-segment LED Nixie tube. The data is from the lower 8 bits DIG\_DATA7\_LO of the DIG7 word data. The bit 0 corresponds to the segment 17 of DIG0, and bit 6 corresponds to the segment 17 of DIG6.

| Bit | Parameter description          | Abbreviation | Bit is 0 (default)                 | Bit is 1                           |

|-----|--------------------------------|--------------|------------------------------------|------------------------------------|

| 0   | Display drive function enable  | DISP         | Turn off display driver            | Allow display driver               |

| 1   | Keyboard scan function enable  | KEYB         | Turn off keyboard scan             | Enable keyboard scan               |

| 3   | Word drive DIG output polarity | DPLR         | Active at low level                | Active at high level               |

| 4   | Scintillation speed/frequency  | SSPD         | Low speed (about 2.3Hz)            | Fast speed (about 4.6Hz)           |

| 6   | XSG pin output enable          | XSOE         | Disable XSG pin output             | Allow XSG pin output               |

| 7   | XSG pin working mode           | XGPO         | XSG is used to extend segment scan | XSG is used for I/O extension GPIO |

# **6.4. Set Display Parameters**: 001010-[MODE][LIMIT][INTENSITY]B

"Set Display Parameters Command" is used to set the display parameters of CH454: decoding MODE, scanning LIMIT, and display INTENSITY. Decoding MODE is controlled by 1-bit data. BCD decoding MODE (XSG does not decode at all) is selected when it's set to 1 for the lower 8 segments SEG7 ~ SEG0, and non-decoding MODE (default value) is selected when it's set to 0. The scan limit is controlled by 3-bit data, and the scan limit of data 001B~111B and 000B is set as 1~7 and 8 respectively (default value). The display brightness INTENSITY is controlled by 4-bit data, and the display drive duty ratio of data 0001B~1111B and 0000B is set as 1/16~15/16 and 16/16 respectively (default value). For example, the command data 001010-01110000B represents the non-decoding mode, the scanning limit is 7, and the duty ratio of display driver is 16/16. The command data 001010-10001010B represents the BCD decoding mode, the scanning limit is 8, and the duty ratio of display driver is 10/16.

#### 6.5. Set Auxiliary Parameters: 000100-1010000[LMTC]B

"Set Auxiliary Parameters Command" is used to set the auxiliary parameters of CH454: segment current limit LMTC. By default, there is no upper limit for the segment output current, and the actual short-circuit current can reach above 80mA. When the current limit of LMTC segment is set to 1, the output current of SEG and XSG segments in CH454 will be limited to 30mA, so that 8 or 16 serial current limiting resistors between the segment drive pins and the LED Nixie tubes can be removed.

# 6.6. Customized BCD Code: 000110-1[SELF\_BCD] B

The customized BCD code command is used to define the special characters that are not realized in regular BCD decoding. CH454 supports a customized BCD code whose BCD value is 1EH. The display code is specified by the command. The coding has 7 bits, corresponding to 7 segments of the LED Nixie tube respectively, and the decimal point is independently controlled by the highest bit of the BCD value. For example, the command data 001110111110B represents the customized BCD character U (the displayed data in the corresponding segment is 3EH). In BCD decoding mode, when the MCU is required to display the BCD value 1EH, CH454 will display the character U in the corresponding LED Nixie tube. When the MCU is required to display the BCD value 9EH, CH454 will display the character U. (including the decimal point) in the corresponding LED Nixie tube.

# 6.7. Set Flash Control: 001100-[D7S][D6S][D5S][D4S][D3S][D2S][D1S][D0S]B

"Set Flash Control Command" is used to set the flash display property of CH454: D7S~D0S correspond to 8 word drive DIG7~DIG0 respectively. The flash property D7S~D0S is controlled by 1-bit data respectively. When the corresponding data bit is set to 1, enable flash display, otherwise it is the normal display without flash (default value). For example: the command data 011000100001B represents that set the flash display of the LED Nixie tubes DIG5 and DIG0, and the rest of the LED Nixie tubes are normally displayed without flash.

# 6.8. Segment Addressing Cleared to 0: 000010-10[BIT ADDR]B

The segment addressing clear to 0 command is used to turn off the LEDs at the specified address (or the designated segment of the LED Nixie tubes). This command can only turn off one LED at the specified address at a time and does not affect the status of other LEDs at all. The sequence of segment addressing is in the same as the key code, which can be subtracted from the key code value by 40H. For example, the command data 000010-10111010B represents that the LED addressed to 3AH is OFF, namely SEG7 of DIG2 LED Nixie tube is OFF.

### **6.9. Segment Addressing Set to 1**: 000010-11[BIT ADDR]B

The segment addressing set to 1 command is used to turn on the LEDs at the specified address (or the designated segment of the LED Nixie tubes). This command can only turn on one LED at the specified address at a time and does not affect the status of other LEDs at all. The sequence of segment addressing is in the same as the key code, which can be subtracted from the key code value by 40H. For example, the command data 000010-11000110B represents that the LED addressed to 06H is ON, namely SEG0 of DIG6 LED Nixie tube is ON.

#### 6.10. Load Word Data Low Byte: 01[DIG ADDR]0-[DIG DATA LO]B

"Load Word Data Low Byte Command" is used to write the low byte DIG\_DATA\_LO of the word data to the data register at the address specified by DIG\_ADDR. DIG\_ADDR specifies the address of the data register through 3-bit data. Data 000B~111B specify the addresses 0 ~ 7 respectively, corresponding to 8 LED Nixie tubes driven by the pins DIG0~DIG7. DIG\_DATA\_LO is the lower 8 bits of 16-bit word data. For example, the command data 010100-01111001B represents that the word data 79H is written to the low byte of the third data register (driven by the DIG2 pin).

### 6.11. Load Word Data High Byte: 10[DIG ADDR]0-[DIG DATA HI]B

"Load Word Data High Byte Command" is used to write the high byte DIG\_DATA\_HI of the word data to the data register at the address specified by DIG\_ADDR. DIG\_ADDR specifies the address of the data register through 3-bit data. Data 000B~111B specify the addresses 0 ~ 7 respectively, corresponding to 8 LED Nixie tubes driven by the pins DIG0~DIG7. DIG\_DATA\_HI is the higher 8 bits of 16-bit word data. For example, the command data 100110-01011011B represents that the word data 5BH is written to the high byte of the fourth data register (driven by the DIG3 pin).

### **6.12. Read SEG Pins**: 000011-[SEG7][SEG6][SEG5][SEG4][SEG3][SEG2][SEG1][SEG0]B

"Read SEG Pin Command" is used to obtain the current state of CH454 SEG7  $\sim$  SEG0 pins, that is, input 8-bit data from the pins.

# 6.13. Read XSG Pins: 000101-[XSG7][XSG6][XSG5][XSG4][XSG3][XSG2][XSG1][XSG0]B

"Read XSG Pin Command" is used to obtain the current state of CH454 XSG7~XSG0 pins, that is, input 8-bit data from the pins.

#### 6.14. Read Customized BCD Code: 000111-0[SELF BCD]B

"Read Customized BCD Code Command" is used to obtain the customized BCD code that was previously written.

# 6.15. Read Back System Parameters: 001001-[XGPO][XSOE]0[SSPD][DPLR]0[KEYB][DISP]B

"Read Back System Parameters Command" is used to obtain the current system-level parameters of CH454.

### 6.16. Read Back Display Parameters: 001011-[MODE][LIMIT][INTENSITY]B

"Read Back Display Parameters Command" is used to obtain the current display parameters of CH454.

# 6.17. Read Back Flash Control: 001101-[D7S][D6S][D5S][D4S][D3S][D2S][D1S][D0S]B

"Read Back Flash Control Command" is used to obtain the current flash display property of CH454.

#### **6.18. Read Key Code**: 001111-[KEY7][KEY6][KEY5][KEY4][KEY3][KEY2][KEY1][KEY0]B

"Read Key Code Commands" is used to get the code for the valid key that CH454 recently detects. Bit 7 of the key code is 0, bit 6 is the status code, bit  $5 \sim$  bit 0 are the scan code and key addressing. For example, if CH454 detects a valid key and interrupts, the MCU sends out a read key code command to CH454 and obtains the key code from CH454. Returns the ID data 2AH if this is the first command after reset.

#### 6.19. Read Back Word Data Low Byte: 01[DIG ADDR]1-[DIG DATA LO]B

"Read Back Word Data Low Byte Command" is used to obtain the low byte data DIG\_DATA\_LO of the data register at the address specified by DIG\_ADDR.

# 7. Parameters

#### 7.1. Absolute Maximum Value

Critical value or exceeding the absolute maximum value may cause the chip to work abnormally or even be damaged.

| Name | Parameter description                                 | Min. | Max. | Unit |

|------|-------------------------------------------------------|------|------|------|

| TA   | Ambient temperature during operation                  | -40  | 85   | °C   |

| TS   | Ambient temperature during storage                    | -55  | 125  | °C   |

| VCC  | Supply voltage (VCC connects to power, GND to ground) | -0.5 | 6.0  | V    |

| VIO   | Voltage on the input or output pins            | -0.5 | VCC+0.5 | V  |

|-------|------------------------------------------------|------|---------|----|

| IMdig | Continuous drive current of single DIG pin     | 0    | 200     | mA |

| IMseg | Continuous drive current of single SEG pin     | 0    | 30      | mA |

| IMall | Total continuous drive current of all SEG pins | 0    | 200     | mA |

# 7.2. Electrical Parameters

Test Conditions: TA=25°C, VCC=5V

| Name   | Parameter description                                | Min. | Тур. | Max.    | Unit |

|--------|------------------------------------------------------|------|------|---------|------|

| VCC    | Power supply voltage                                 | 2.8  | 5    | 5.3     | V    |

| ICC    | Current of power supply                              | 2    | 50   | 150     | mA   |

| Islp5  | 5V low power sleep current (all I/O suspended)       |      | 0.08 |         | mA   |

| Islp3  | 3.3V low power sleep current (all I/O suspended)     |      | 0.03 |         | mA   |

| VILseg | Low level input voltage of SEG and XSG pins          | -0.5 |      | 0.5     | V    |

| VIHseg | High level input voltage of SEG and XSG pins         | 1.8  |      | VCC+0.5 | V    |

| VIL    | Remaining pins low level input voltage               | -0.5 |      | 0.8     | V    |

| VIH    | Remaining pins high level input voltage              | 2.0  |      | VCC+0.5 | V    |

| VOLdig | Low level output voltage of DIG pin (-120mA)         |      |      | 0.8     | V    |

| VOHdig | High level output voltage of DIG pin (8mA)           | 4.5  |      |         | V    |

| VOLseg | Low level output voltage of SEG and XSG pins (-20mA) |      |      | 0.5     | V    |

| VOHseg | High level output voltage of SEG and XSG pins (20mA) | 4.5  |      |         | V    |

| VOL    | Low level output voltage of other pins (-4mA)        |      |      | 0.5     | V    |

| IDN1   | Input pull-down current of SEG pin                   | -30  | -80  | -400    | uA   |

| IDN0   | Input pull-down current of RSTI pin                  | -80  | -140 | -200    | uA   |

| IUP0   | Input pull-up current of XSG pin                     | 10   | 20   | 300     | uA   |

| IUP1   | Input pull-up current of SCL pin                     | 30   | 80   | 150     | uA   |

| IUP2   | Input and output pull-up current of SDA pin          | 60   | 100  | 200     | uA   |

| IUP3   | Output pull-up current of INT# pin                   | 500  | 3500 | 5000    | uA   |

| VR     | Default voltage threshold of power on reset          | 2.0  | 2.3  | 2.7     | V    |

# 7.3. Internal Timing Parameters

Test Conditions: TA=25°C, VCC=5V

(Note: The timing parameters in this table are multiples of the built-in clock cycle, and the frequency of the built-in clock may be affected by the supply voltage)

|      | 111                                                                          |      |      |      |      |

|------|------------------------------------------------------------------------------|------|------|------|------|

| Name | Parameter description                                                        | Min. | Тур. | Max. | Unit |

| TPR  | Power on reset time of power supply                                          | 3    | 10   | 50   | mS   |

| TSLP | The time between receiving the sleep command and the official start of sleep | 8    | 20   | 60   | uS   |

| TWK  | The time to be awakened to resume work during sleep                          | 10   | 100  | 200  | uS   |

| TDP  | Display scanning cycle (when the scanning limit is 8) | 4   | mS |

|------|-------------------------------------------------------|-----|----|

| FSPS | Frequency of flash display (slow/default)             | 2.3 | Hz |

| TKS  | Keyboard scanning interval, key response time         | 30  | mS |

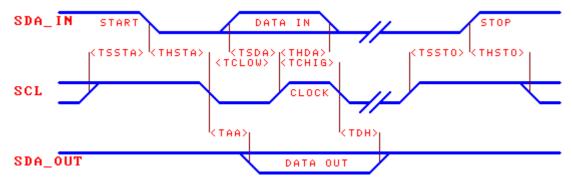

### 7.4. Interface Timing Parameters

Test Conditions: TA=25°C, VCC=5V, Refer to the Attached Drawing)

| Name  | Parameter description                                | Min. | Typ. | Max. | Unit |

|-------|------------------------------------------------------|------|------|------|------|

| TSSTA | Setup time of SDA falling edge start signal          | 200  |      |      | nS   |

| THSTA | Hold time of SDA falling edge start signal           | 200  |      |      | nS   |

| TSSTO | Setup time of SDA rising edge stop signal            | 200  |      |      | nS   |

| THSTO | Hold time of SDA rising edge stop signal             | 200  |      |      | nS   |

| TCLOW | Low level width of SCL clock signal                  | 200  |      |      | nS   |

| TCHIG | High level width of SCL clock signal                 | 200  |      |      | nS   |

| TSDA  | Setup time of SDA input data to SCL rising edge      | 30   |      |      | nS   |

| THDA  | Hold time of SDA input data to SCL rising edge       | 10   |      |      | nS   |

| TAA   | Delay SDA output data to SCL falling edge            | 2    |      | 30   | nS   |

| TDH   | Delay of invalid SDA output data to SCL falling edge | 2    |      | 40   | nS   |

| Rate  | Average data transmission rate                       | 0    |      | 2M   | bps  |

# 8. Application

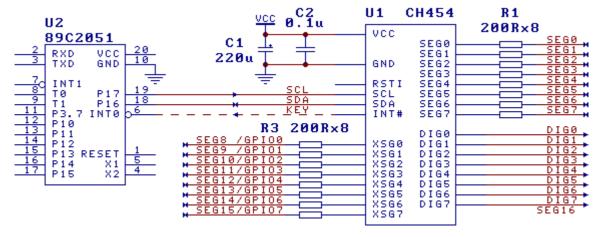

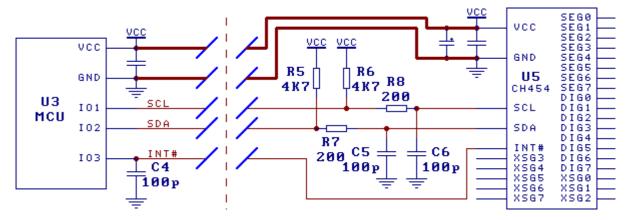

## **8.1. Connection to MCU** (Figure below)

CH454 is connected to the MCU U2 through two-wire serial interfaces. Capacitors C1 and C2 are arranged near the power pins of U1 to decouple the power supply and reduce the interference caused by driving high current. When the keyboard function is not needed, the KEY signal line can be removed and only the SCL and SDA two signal lines can be used. When the keyboard function is used, the KEY signal line of INT# pin of CH454 can be connected to the interrupt input pin of the MCU or the ordinary I/O pin for inquiry.

If the segment current limiting LMTC function of CH454 is enabled, then the segment current limiting resistors R1 and R3 can be removed; otherwise, it is necessary to connect R1 and R3 in series for the segment drive pins to limit and balance the drive current of each segment. The greater the resistance of the series current limiting resistor is, the smaller the segment drive current is, and the lower the display brightness of the LED Nixie tube is. The resistance of R1 or R3 is generally between  $50\Omega$  and  $1K\Omega$ . Under the same other conditions, a higher resistance value should be preferred. At the supply voltage of 5V, the

corresponding segment current is usually 13mA when the series resistance is  $200\Omega$ .

Since some I/O pins of the standard MCS51 MCU is weak pull-up quasi bidirectional ports, it is recommended to add the pull-up resistors to SCL and SDA to reduce interference in the circuit that is remotely connected to CH454. The resistance of the pull-up resistor can be from  $1K\Omega$  to  $10K\Omega$  and the pull-up resistor is not required for the close range. The farther the distance is, the smaller the resistance should be.

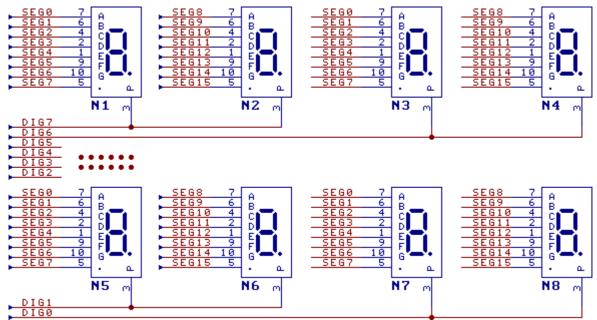

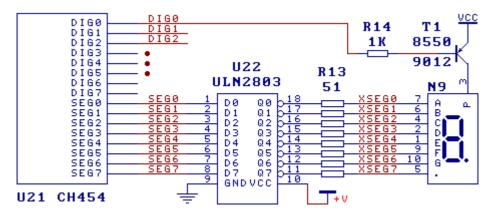

#### **8.2. Drive Common Cathode LED Nixie tube** (as Shown Below)

CH454 can dynamically drive 8 16-segment common cathode LED Nixie tubes. If the number of LED Nixie tubes is less than 8, then the LED Nixie tubes driven by DIG7, DIG6, DIG5 and DIG4 can be removed in sequence, and the corresponding scanning limit can be set to obtain a higher dynamic drive current, so as to improve the display brightness.

CH454 can also dynamically drive 16 8-segment common cathode LED Nixie tubes (refer to the figure below). If only 8 8-segment common cathode LED Nixie tubes need to be driven, then the redundant XSG0 ~ XSG7 pins can be used for general-purpose I/O extension, which can be used to extend the I/O pins of the MCU system.

If the keyboard scan function of CH454 is used simultaneously, considering the reverse leakage of some LED Nixie tubes at high working voltage, it is easy for CH454 to mistake that a key has been pressed down, so it is recommended to connect the LEDs in series at the common cathode of the LED Nixie tubes to prevent the reverse leakage, and to improve the level of input signals SEG0-SEG7 during keyboard scan to ensure more reliable keyboard scan. When the supply voltage is low (e.g. VCC=3.3V), these LEDs should be removed to avoid affecting the display brightness.

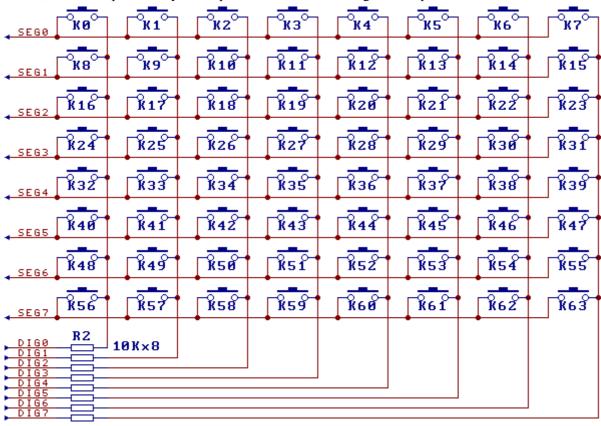

#### 8.3. 8×8 Keyboard Scan (Figure below)

CH454 has a 64-key keyboard scan function. If only a few keys are needed in the application, any unused keys can be removed from  $8\times8$  matrix. In order to prevent short circuit from being formed between SEG signal line and DIG signal line to impact display after the key is pressed, the current limiting resistor R2 should be connected in series between CH454 DIG0~DIG7 and the keyboard matrix, and their resistance can be from  $2K\Omega$  to  $15K\Omega$ . If the MCU enables CH454 to enter the low-power sleep state and the keyboard scan function of CH454 was previously started, then CH454 in sleep state can be waked up by the keys K0~K31, and it will provide key interrupt for the MCU after being waked up.

#### **8.4. Drive Common Anode LED Nixie tube** (as Shown Below)

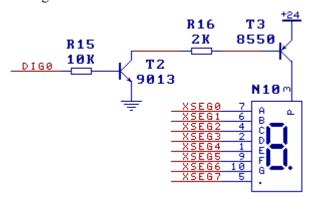

If the segment drive signals SEG0  $\sim$  SEG7, XSG0  $\sim$  XSG7 and the word drive signals DIG0  $\sim$  DIG7 are inverted respectively, then the common anode LED Nixie tube can be driven, but the keyboard function is not supported. In the figure below, the segment signals SEG0  $\sim$  SEG7 are reversely driven by U22 Darlington array, and can also be replaced by 8 NPN triodes whose bases are connected with the current limiting resistor in series. The word signals DIG0  $\sim$  DIG7 are reversely driven by 8 PNP triodes T1. If U22 itself does not support constant current drive, then the resistor R13 is used to limit and balance the segment current. The drive current of this circuit is several times larger than that of the common cathode LED Nixie tube directly driven by CH454. Corresponding resistance values should be selected for the resistors R13 and R14 in the figure according to the actual drive current.

In order to save costs, the U22 in the figure below can also be removed and the segment pins are directly driven by CH454. However, the loaded word data must be reversed by bit (0 ON and 1 OFF). It is recommended to load all the word data 0FFH before starting the display.

For the large size LED Nixie tube composed of multiple LEDs in series, due to its large voltage drop, the 5V supply voltage cannot be driven directly. Usually it needs to be connected to the high voltage drive circuit. In the figure below, the output polarity of CH454 word drive DIG is set as "active at high level" and then the 24V drive voltage is output after twice phase inversion of NPN triode T2 and PNP triode T3. In combination with the segment inverting drive circuit U22 in the figure above, the large-size common anode LED Nixie tube with high voltage can be driven. Corresponding resistance value should be selected for the resistor R16 in the figure according to the actual drive current size.

#### **8.5.** Anti-interference and Manual Reset (Important)

CH454 has a built-in power on reset function. During the normal operation of CH454, the RSTI pin can be used for manual reset input. When high level is input by RSTI, the CH454 chip is reset. If the RSTI is connected to the instrument panel as a manual reset input, in order to reduce external interference, it is recommended to connect a capacitor between the RSTI pin and ground GND with a capacity from 1000pF and 0.1UF.

As CH454 drives the LED Nixie tube or LED has high current, high glitch voltage will be generated on the power supply. Therefore, if the PCB wiring of the power line or ground wire is not reasonable, it may affect the stability of the MCU or CH454. Solutions to power interference:

- ① It is recommended to use shorter and thicker power line and ground wire, especially when CH454 and the MCU are arranged on two PCBs;

- The power supply decoupling capacitor is connected in parallel close to the CH454 between the positive and negative power supplies. At least one 0.1uF leaded multilayer ceramic capacitor or ceramic capacitor and one electrolytic capacitor with a capacity of not less than 100uF.

For external interference when the signal line is long, refer to the following figure for solution:

- ① At the pin end close to CH454 on the signal line, add the capacitors C5 and C6 with the capacitance of 47pF to 470pF. If the capacitance is higher, the transmission speed of the communication interface for the MCU will be lower.

- ② Optionally add the resistors R7 and R8 with resistance of  $100-470\Omega$ ;

- 3 Reduce the transmission speed between the MCU and CH454 (because of added resistance and capacitance);

④ If it is driven by a quasi-bidirectional I/O pin (such as standard MCS51 MCU), it will be suggested to add resistors R5 and R6 with resistance of 500Ω to 10KΩ to strengthen the pull-up capacity of the quasi-bidirectional I/O pin for MCS-51 MCU, so as to keep good digital signal waveform during long distance transmission. Pull-up resistors R5 and R6 are not required for short signal lines, and pull-up resistors R5 and R6 are not required for bidirectional I/O pins driven by totem pole.

In addition, for the application environment with strong interference, the MCU can refresh CH454 every a few seconds, including reloading the data register of each LED Nixie tube and restarting the display.

### 8.6. MCU Interface Program

The website provides the common C program language and ASM assembly interface program for the MCU.